Phương pháp không phân rã trong đề xuất được phân thành hai dạng chính: “không xâm lấn” và “xâm lấn”. Các kỹ thuật “không xâm lấn” không thay thế thiết kế ban đầu của IC, trong khi các kỹ thuật “xâm lấn” thay đổi thiết kế, để nhúng các tính năng nhằm mục đích phát hiện HT.

Các kỹ thuật phát hiện HT xâm lấn có thể được phân loại tiếp thành 2 dạng: Thứ nhất là theo hướng chèn HT trong quá trình thiết kế hoặc chế tạo vi mạch; Thứ hai là HT được chèn trong quá trình kiểm tra vi mạch sau khi được sản xuất. Nghiên cứu [5] đã chỉ ra việc chèn HT phụ thuộc vào không gian trống của vi mạch sau bước sắp xếp các thành phần linh kiện trên mạch (layout), vì toàn bộ diện tích của vi mạch không thể được thay đổi bởi nhà sản xuất. Tuy nhiên, nếu nhà sản xuất có khả năng trích xuất thiết kế ở mức cổng logic (gate-netlist) từ thiết kế mức layout, thông qua việc tối ưu hóa logic và các kỹ thuật sắp xếp và định tuyến tốt hơn, thì có thể giải phóng không gian để chứa HT.

Một kỹ thuật thiết kế và quy trình tự động hóa thiết kế liên quan được đề xuất trong [6] để ngăn chặn hiệu quả việc chèn HT. Trong kỹ thuật này, thiết kế ban đầu được xáo trộn thông qua việc mở rộng không gian trạng thái có thể tiếp cận nhằm gây khó khăn cho nhà sản xuất trong việc dịch ngược chức năng của mạch và tìm các kẽ hở hiếm có. Các HT được chèn vào một thiết kế mà không xem xét đến hành vi chức năng thực sự của nó sẽ trở nên không hợp lệ (tức là không được kích hoạt trong chế độ hoạt động bình thường) hoặc có thể dễ dàng bị phát hiện. Phương pháp này cải thiện đến 24% trong việc phát hiện HT với chi phí thiết kế ít hơn 10%.

Các kỹ thuật thiết kế cũng có thể được sử dụng để hỗ trợ việc phát hiện HT bằng cách kiểm tra logic hoặc các phép đo kênh bên. Vì nhà sản xuất có khả năng khai thác các điều kiện bên trong vi mạch để tạo ra HT, nên có một phương pháp thiết kế nhằm tăng khả năng kiểm soát và khả năng quan sát các điều kiện bên trong vi mạch để tăng phạm vi phát hiện HT. Trong [7], mỗi mô-đun trong một thiết kế được sửa đổi sao cho một chuỗi tín hiệu đầu vào cụ thể kích hoạt một máy trạng thái hữu hạn (Finite State Machine - FSM) được nhúng trong mô-đun để đưa về chế độ đặc biệt gọi là chế độ trong suốt (Hình 1a). Trong chế độ này, khả năng kiểm soát và khả năng quan sát của các nút tải và bộ kích hoạt HT có thể xảy ra được nâng cao và một tín hiệu nén ở các đầu ra chính cho biết có hoặc không sự tồn tại của HT.

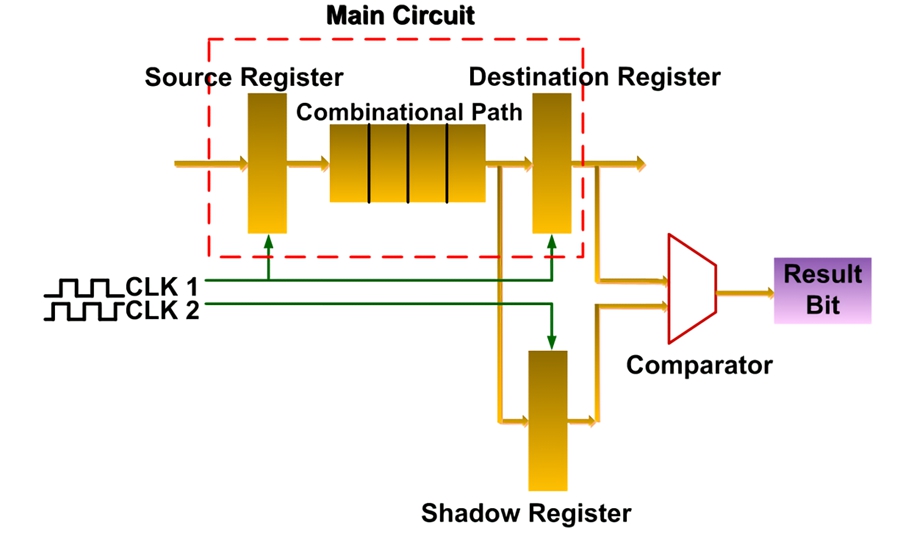

Trong [8], đề xuất một kỹ thuật thiết kế gọi là VITAMIN dựa trên giá trị nghịch đảo của điện áp cấp của các mức logic thay thế trong vi mạch. Hành vi logic của cổng logic hoạt động với điện áp cung cấp ngược được đảo ngược trong chế độ kiểm tra. Kết quả là hoạt động của một mạch HT được kích hoạt được tăng cường và có thể được phát hiện bằng cách so sánh cấu hình nguồn của các vi mạch khác nhau. Trong [9], các tác giả đề xuất một kỹ thuật mô tả đặc tính trễ “ở tốc độ” có khả năng phát hiện các sửa đổi đối với mạch, cả ở thời gian chạy và thời gian thử nghiệm. Đặc tính trễ của đường dẫn dựa trên việc chèn các “mạch chốt” (Hình 1b) trong thiết kế để thu thập và so sánh với dữ liệu được chốt bởi các thanh ghi trong các đường dẫn mạch gốc. Các phép đo thời gian thử nghiệm được so sánh với các giá trị dự kiến của thời gian thiết kế và bất kỳ sự khác biệt thống kê đáng kể nào cũng chỉ ra sự thay đổi thiết kế có mã độc. Trong [10], phương pháp này đã được chứng minh là có khả năng phát hiện HT trong mạch nhân mảng 8×8 với các thay đổi quy trình khoảng ± 20%. Một kỹ thuật chèn flip-flop giả để tăng xác suất kích hoạt của HT đã được trình bày trong [11], để hỗ trợ việc phát hiện HT thông qua các kỹ thuật kênh bên. Nó cũng có thể giúp phát hiện HT với kiểm tra logic bằng cách làm cho tác động độc hại của HT có thể quan sát được ở đầu ra chính.

Một kỹ thuật mới khác được đề xuất trong [12] là sử dụng công nghệ vi mạch 3-D để tích hợp các cơ chế bảo mật trong một mặt phẳng riêng biệt (gọi là mặt phẳng điều khiển) bên trên mặt phẳng mạch hiện có trong một vi mạch (gọi là mặt phẳng tính toán). Trong đó, một số cơ chế bảo mật được thực hiện bởi mặt phẳng điều khiển. Tuy nhiên, nghiên cứu này không thảo luận về những thách thức kỹ thuật và chi phí thiết kế.

Kỹ thuật phát hiện HT “không xâm lấn”

Trong các kỹ thuật phát hiện HT không “không xâm lấn”, HT được phát hiện bằng cách so sánh hành vi của IC kiểm tra với mô hình IC mẫu (hay còn được gọi là mô hình “vàng”). Kỹ thuật này có thể được phân loại thành hai loại: theo thời gian chạy (runtime) và theo thời gian kiểm tra (test-time). Các kỹ thuật run-time khai thác một hệ thống giám sát trực tuyến cố gắng để phát hiện hoạt động nghi ngờ trong quá trình vận hành. Trong khi các kỹ thuật test-time được hướng tới việc phát hiện các chip bị nhiễm HT trước khi triển khai.

- Phát hiện theo thời gian chạy: Trong [13], các tác giả đề xuất bổ sung logic Thiết kế kích hoạt bảo mật (DEFENSE) có thể tái cấu hình trong một hệ thống trên chip nhất định để cho phép giám sát chức năng thời gian thực. Việc kiểm tra có thể được thực hiện đồng thời với hoạt động bình thường của mạch và kích hoạt các biện pháp đối phó phù hợp khi phát hiện ra sự sai lệch so với chức năng bình thường. Tuy nhiên, hiệu quả và chi phí phần cứng liên quan đến phương pháp này không được đề cập đến. Trong [14], các tác giả đề xuất một kiến trúc bus SoC mới có thể phát hiện các hành vi bus độc hại liên quan đến phần cứng HT, bảo vệ hệ thống và bus hệ thống khỏi các độc hại này và báo cáo các hành vi độc hại cho CPU hệ thống mà không làm mất hiệu suất của bus. Các tác giả báo cáo số lượng cổng bổ sung thêm khoảng 800 cổng logic trong một SoC có 4 triệu cổng và độ trễ không đáng kể.

Trong [15], các tác giả đề xuất một phương pháp mà theo đó các phiên bản phần mềm tương đương về chức năng được thực thi trên nhiều lõi CPU, được hỗ trợ bởi lập lịch phần mềm phân tán động. Các kết quả đầu ra của tác vụ nhỏ từ các lõi khác nhau được so sánh để đánh giá động các cấp độ tin cậy riêng lẻ của các lõi, với bộ lập lịch phân tán trải qua quy trình học tập tin cậy cho nhiều lần chạy. Các tác giả cho thấy rằng phương pháp này có khả năng hoàn thành tốt các tác vụ trong một môi trường bị nhiễm HT, với sự cải thiện về thông lượng qua các lần chạy liên tiếp.

Cách tiếp cận kết hợp phần cứng và phần mềm để thực hiện giám sát việc thực thi thời gian chạy đã được đề xuất trong [16 - 17]. Ở đây, mô-đun “bảo vệ phần cứng” có thể xác minh đơn giản bên ngoài CPU được xem xét đến. Công việc chủ yếu nhắm vào các cuộc tấn công DoS và leo thang đặc quyền, sử dụng các kiểm tra định kỳ của hệ điều hành được tăng cường với chức năng kiểm tra trực tiếp. Các tác giả báo cáo chi phí hiệu suất trung bình 2,2% bằng cách sử dụng các chương trình chuẩn SPECint 2006, nhưng không báo cáo chi phí thiết kế phần cứng.

- Phát hiện theo thời gian kiểm tra: Có 2 cách tiếp cận chính dựa trên thử nghiệm để phát hiện HT: dựa trên thử nghiệm logic và phương pháp dựa trên phép đo các thông số kênh kề. Ưu điểm chính của các kỹ thuật test-time so với các kỹ thuật run-time là không yêu cầu cao về phần cứng. Nhưng nhược điểm chính là yêu cầu một IC chuẩn (tức là không chứa HT) hoặc mô hình chức năng. Các phương pháp run-time thường liên quan đến hiệu suất và công suất tiêu thụ, tuy nhiên, cung cấp tuyến phòng thủ cuối cùng và có khả năng cung cấp 100% độ tin cậy trong kết quả được tính toán.

+ Phương pháp dựa trên kiểm tra logic: thách thức chính của phương pháp này là không gian HT phải rất lớn để tạo ra tập đầy đủ các véc tơ kiểm tra đủ để phát hiện các HT.

+ Phương pháp phát hiện dựa trên phép đo các thông số kênh bên: dựa trên việc quan sát ảnh hưởng của một HT được chèn vào một tham số vật lý như quá độ dòng điện mạch, mức tiêu thụ điện hoặc độ trễ đường dẫn. Ưu điểm của các cách tiếp cận này là ngay cả khi mạch HT không gây ra sự cố trong quá trình chạy thử nghiệm, thì sự tồn tại của mạch HT vẫn có thể được phát hiện thông qua sự ảnh hưởng lên các tham số vật lý của kênh phụ. Tuy nhiên, các thách thức chủ yếu liên quan đến phân tích kênh phụ là sự thay đổi lớn trong quá trình thực hiện của các công nghệ nano hiện đại, các phép đo nhiễu làm giảm đi ảnh hưởng của mạch HT, đặc biệt là với các mạch HT nhỏ.

Trong [18], các tác giả đã đưa ra khái niệm về “dấu vân tay IC”, trong đó mỗi IC được kết hợp với một chữ ký, hay còn được gọi là “dấu vân tay” bằng cách đo một hoặc nhiều tham số kênh bên. Từ việc phân tích các dấu vết nguồn điện, được sử dụng làm dấu vân tay IC trong nghiên cứu này, các tác giả có khả năng xác định các HT có diện tích nhỏ tương đương bằng 0,01% tổng kích thước của mạch, với sự thay đổi của các tham số ngẫu nhiên vào khoảng ± 7,5%. Một cách tiếp cận khác dựa trên phép đo tín hiệu nguồn điện cấp tức thời được mô tả trong [19], trong đó các tín hiệu từ nhiều cổng nguồn cho các IC được đo thông qua quá trình hiệu chuẩn và các đặc tính thống kê. Kỹ thuật này có khả năng phát hiện khoảng 50% HT đã kích hoạt và 30% HT không hoạt động trong mạch chuẩn ISCAS-85 (xem Hình 2a).

Trong [20], các tác giả đề xuất phương pháp tạo vector kiểm tra để tối đa hóa hoạt động trong các phân vùng riêng của mạch, đồng thời giảm thiểu hoạt động của các phân vùng khác. Các kết quả mô phỏng giả định sự thay đổi của quy trình lên đến 7,5% thì có thể phát hiện thành công hầu hết các HT được chèn trong mạch.

Độ trễ đường dẫn của các cổng đầu ra được sử dụng làm dấu vân tay được chỉ ra trong [21], với đặc trưng mở rộng cho các thay đổi trong quá trình thực hiện. Quy trình này có thể phát hiện HT có diện tích chỉ chiếm 0,13% tổng diện tích với 7,5% các thay đổi trong quá trình thực hiện (xem Hình 2b), trong khi đối với HT có diện tích chiếm 0,36% tổng diện tích, tỷ lệ phát hiện là 36%. Cả hai tham số độ trễ đường truyền và dòng rò đều được xem xét đến trong kỹ thuật mức cổng logic được đề xuất trong [22], trong đó vấn đề phát hiện được tổng quát hóa như vấn đề lập trình tuyến tính (Linear Programming Problem). Các tác giả chỉ ra rằng kỹ thuật này có khả năng phát hiện HT trong các mạch chuẩn ISCAS-85 với độ tin cậy cao.

Tuy nhiên, kỹ thuật này không có khả năng phát hiện đối với các thiết kế tuần tự cỡ lớn. Phần lớn các phương pháp tiếp cận kênh phụ đã công bố cung cấp các kết quả xác minh mô phỏng. Các thay đổi trong quá trình thực hiện, các dung sai trong thiết kế, và các độ nhiễu phụ thuộc vào nhiều tham số và khó để mô hình hóa một cách chính xác. Do đó, trong cách tiếp cận kênh phụ, việc xác định tính chính xác của phần cứng là quan trọng để phân tích chính xác việc phát hiện HT. Bảng 1 tóm tắt những ưu điểm và nhược điểm của phương pháp kiểm tra logic và phương pháp kênh phụ để phát hiện HT. Bảng này cũng chỉ rõ 2 phương pháp tiếp cận này bổ sung cho nhau về khả năng phát hiện HT. Do đó, các cách tiếp cận kết hợp các ưu điểm của cả hai có thể là giải pháp hứa hẹn nhất về khả năng phát hiện HT nói chung.

Kết luận

HT và các phép đo hiệu quả để tìm ra mã độc này là mối quan tâm lớn trong thời gian gần đây. Bài báo đã trình bày về phương pháp phát hiện HT không phân rã. Dựa trên việc xem xét tính chất tự nhiên bị thay đổi và kích thước của Trojan, sự kết hợp của các kỹ thuật trong cả quá trình thiết kế và kiểm tra đặt ra yêu cầu để cung cấp độ bảo mật ở mức chấp nhận được cho các mạch phần cứng. Các phương pháp dựa trên thời gian thiết kế mở ra các mức mô tả thiết kế khác nhau.

Mặt khác, việc xác định tính chính xác của mạch sau khi thiết kế yêu cầu sự kết hợp của cả hai phương pháp kiểm tra kênh phụ và kiểm tra logic để phát hiện được các dạng HT và kích thước HT khác nhau dưới điều kiện các tham số thay đổi lớn. Các thách thức chủ yếu trong thời gian tới về lĩnh vực này bao gồm việc phát triển các cơ chế phát hiện HT trong các mạch tương tự mà có thể thực hiện nhiều dạng kích hoạt và điều kiện quan sát khác nhau; một tham số tích hợp được độ tin cậy của cả hai phương pháp thiết kế và kiểm tra; và một nền tảng tính toán mà phân tích một thiết kế để xác định các khu vực có lỗ hổng và tác động của việc thay đổi thiết kế lên độ tin cậy đạt được.